QuestaSim SE是一款非常好用且功能强大的由Mentor Graphics公司推出的高级仿真模拟软件,软件基于标准的单核验证引擎,集成了一个HDL模拟器,一个约束求解器,一个判断引擎,功能覆盖,以及一个通用的用户界面,可以用于各类产品的仿真模和调试等操作,可以大大地降低复杂FPGA和SOC设计的风险,需要此款工具的伙伴们欢迎前来下载使用。

更新说明

改进了SystemVerilog TB / OVM / UVM的性能和错误消息;

改进了VHDL和混合VHDL / Verilog的性能;

提高了Altera和Xilinx VHDL库组件的性能;

新增加的工具栏用于改善GUI(这由编辑首选项控制);

对VHDL动态访问类型的新调试支持;

为新的Visualizer调试环境创建本机设计数据库和波形数据库;

对SystemC 2.3的新支持(Questa Prime或Questa Core的选项);

运行管理器(VRM)容量改进,主动网格作业检查,以及运行时新的设计自动化(RTDA)网格支持;

新的覆盖自动保存,加上数据库容量和性能改进,为合并时间提供数量级的改进;

提高HTML性能,减少内存使用和更改报表控制;

增强对Liberty库模型和属性(PA)的支持;

增强对嵌入式开关和供应相关属性(PA)的分析和仿真支持;

支持新的Visualizer调试环境(PA);

提训容量和性能等。

使用教程

1.建立work库

在Transcript中输入命令vlib work,此时work库是空的。

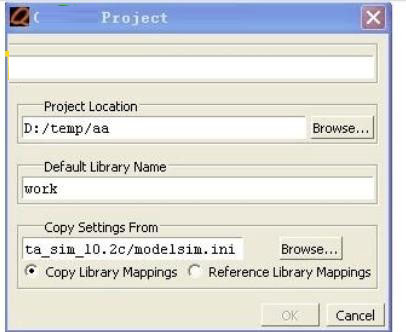

2.File→New→project

建立工程,填写工程名sat1。

2添加已经存在的.V文件,sat.v和sat_tb.v

3.进行编译(vlog编译命令)

在Transcript中输入命令vlog +acc vlog +acc D:/temp/aa/*.v

+acc 去掉一些杂质,保留下所有该保留的东西。 4.进行仿真

vsim test_sat (test_sat是自动生成的,有的也不会自动生成一样的名字的,但会生成相应功能不同名字的文件,此文件不可读,属于机器文件,如果没有成成test_sat,则点击library→sat_tb)

右键点击test_sat,add to→wave→All items in design

5. run 100ns

6. 或者add wave –r/*

点击此键 zoom full

- CNKI全球学术快报(学术报纸阅读平台) for iPhone v4.0 苹果手机版

- 小说规则捕捉器 v3.7.0 中文绿色版

- KuCoin库币交易所 for Android v3.80.2 安卓版

- 烁光投屏大师(手机投屏工具) for Android v1.2.0 安卓手机版

- 开源工具包OpenSSL 3.0 官方最新正式版(含安装方法)

- 博创茶叶采收管理系统 v1.2010.8 中文安装版

- JetBrains DataSpell(数据科学IDE) 2024.3 官方中文安装版

- 熊猫看书(小说阅读软件) for iPhone v9.2.2 苹果手机版

- Windows11一键修复IE11工具 V1.0 绿色便携免费版

- 遇见单词(单词翻译插件)V1.0 免费版

- 迅捷OCR文字识别软件 for Mac V8.5.8 苹果电脑版

- 卫星实景地图 for Android V1.0.0 安卓手机版

- 北极星导航地图 for Android V1.0.1 安卓手机版

- 中表 for android v2.4.14 安卓手机版

- 六寸地球(位置查询)for Android V2.0.1 安卓手机版

- 极速WiFi钥匙 for Android v1.0 安卓版

- Vimeo Record(录屏插件) v1.16.0 免费安装版 附安装说明

- Easy Retouch(ps精修磨皮插件) v1.0 免费汉化版

- 简单图片文字识别提取 v1.0 免费绿色版

- Free Cut Video(视频剪切工具) v1.06 官方安装版

- Sapling(语法检测插件) v3.1.0.7 免费版 附安装方法

- 全能萌拍相机 for Android v15.0.0 安卓版

- 捷效办公 for Android v2.4.9 安卓手机版

- TSC G-220A打印机驱动 v2020.1.4 免费安装版

- 论论 for Android v1.0.0 安卓手机版

- 阿加雷斯特战记2汉化补丁 v2.0 免费版

- 疾风之刃客户端 专属极速下载器 v1.5.424.1 官方免费版

- 策略数块Tactile v1.13 安卓版

- 冠军级别疯狂奔跑 v1.0.0 安卓版

- 太空飞棋 v1.0.0.1 安卓版

- 华丽打砖块2 v1.1.2 安卓版

- 守护冰凌峰1.5A轮回之恋(附隐藏英雄密码)

- 嘴炮大作战 v1.0.0.0 安卓版

- 海贼王-时代的变迁1.6正式版(附隐藏英雄密码)

- 抓兔子Catch The Rabbit v1.0.0 安卓版

- except as

- rare exception

- the only exception

- possible exception

- make an exception

- system exception

- except for

- without exception

- excess mortality

- to excess

- PHP 无刷新添加留言的Ajax实例

- php使用Iframe无刷新上传的代码

- PHP仿Twitter里的Ajax限制字符输入数量的实例

- PHP+Ajax 无刷新登录及注册实例

- PHP+Mysql 老外写的类似祝福墙的Ajax程序

- Google Wave History Ajax无刷新评论带头像

- 凌讯php投票系统程序 v1.0

- PHPCMS v9.6.3 GBK

- PHPCMS v9.6.3 UTF8

- asp百度收藏夹(仿腾讯微博) v2.9